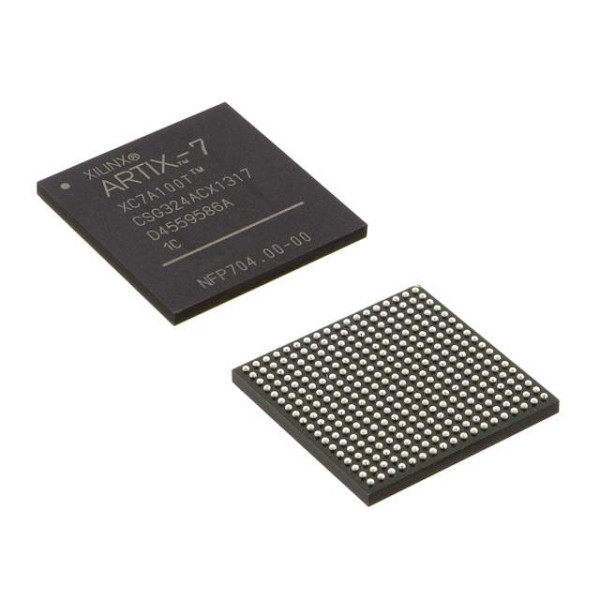

XC7A50T-2CSG324I FPGA – Програмована вентильна матриця XC7A50T-2CSG324I

♠ Опис продукту

| Атрибут продукту | Значення атрибута |

| Виробник: | Ксілінкс |

| Категорія продукту: | FPGA - програмована вентильна матриця |

| Серія: | XC7A50T |

| Кількість логічних елементів: | 52160 ЛЕ |

| Кількість вводів/виводів: | 210 вводів/виводів |

| Напруга живлення - Мін.: | 0,95 В |

| Напруга живлення - макс.: | 1,05 В |

| Мінімальна робоча температура: | - 40°C |

| Максимальна робоча температура: | +100°C |

| Швидкість передачі даних: | - |

| Кількість приймачів: | - |

| Стиль монтажу: | Поверхневий монтаж/поверхневий монтаж |

| Пакет / Корпус: | CSBGA-324 |

| Бренд: | Ксілінкс |

| Розподілена оперативна пам'ять: | 600 кбіт/с |

| Вбудована блокова оперативна пам'ять - EBR: | 2700 кбіт/с |

| Чутливість до вологи: | Так |

| Кількість блоків логічного масиву - LAB: | 4075 ЛАБ |

| Робоча напруга живлення: | 1 В |

| Тип продукту: | FPGA - програмована вентильна матриця |

| Кількість у заводській упаковці: | 1 |

| Підкатегорія: | Програмовані логічні мікросхеми |

| Торгова назва: | Артікс |

| Вага одиниці: | 1 унція |

♠ ПЛІС серії Xilinx® 7 складаються з чотирьох сімейств ПЛІС, які відповідають повному спектру системних вимог, починаючи від низької вартості, малого форм-фактора, економічно чутливих, високопродуктивних застосувань і закінчуючи надвисокою пропускною здатністю з'єднання, логічною ємністю та можливостями обробки сигналів для найвимогливіших високопродуктивних застосувань.

ПЛІС Xilinx® серії 7 складаються з чотирьох сімейств ПЛІС, які відповідають повному спектру системних вимог, починаючи від низької вартості, малого форм-фактора, економічно чутливих, високопродуктивних застосувань і закінчуючи надвисокою пропускною здатністю з'єднання, логічною ємністю та можливостями обробки сигналів для найвимогливіших високопродуктивних застосувань. ПЛІС серії 7 включають:

• Сімейство Spartan®-7: Оптимізовано для низької вартості, найнижчого енергоспоживання та високої продуктивності вводу/виводу. Доступні в недорогому, дуже компактному форм-факторі для найменшої займаної площі друкованої плати.

• Сімейство Artix®-7: Оптимізовано для застосувань з низьким енергоспоживанням, що потребують послідовних приймачів-передавачів та високої пропускної здатності цифрового сигнального процесора (DSP) та логічних процесорів. Забезпечує найнижчу загальну вартість матеріалів для високопродуктивних застосувань з високим рівнем витрат.

• Сімейство Kintex®-7: Оптимізовано для найкращого співвідношення ціни та якості з удвічі кращим результатом порівняно з попереднім поколінням, що дозволяє створювати новий клас ПЛІС.

• Сімейство Virtex®-7: Оптимізовано для найвищої продуктивності та потужності системи з подвійним покращенням продуктивності системи. Пристрої з найвищими можливостями завдяки технології багатошарових кремнієвих з'єднань (SSI).

Побудовані на основі сучасної, високопродуктивної, низькоенергійної (HPL) 28-нм технології метал-гейту з високим k (HKMG), FPGA 7-ї серії забезпечують безпрецедентне підвищення продуктивності системи завдяки пропускній здатності вводу/виводу 2,9 Тбіт/с, ємності 2 мільйони логічних комірок та цифровому сигнальному процесору (DSP) 5,3 TMAC/с, споживаючи при цьому на 50% менше енергії, ніж пристрої попереднього покоління, пропонуючи повністю програмовану альтернативу ASSP та ASIC.

• Удосконалена високопродуктивна логіка FPGA на основі реальної технології 6-вхідних таблиць пошуку (LUT), яку можна налаштувати як розподілену пам'ять.

• 36 Кбіт/с двопортова блочна оперативна пам'ять із вбудованою логікою FIFO для буферизації даних на кристалі.

• Високопродуктивна технологія SelectIO™ з підтримкою інтерфейсів DDR3 до 1866 Мбіт/с.

• Високошвидкісне послідовне з’єднання з вбудованими багатогігабітними приймачами від 600 Мбіт/с до максимальної швидкості 6,6 Гбіт/с до 28,05 Гбіт/с, що пропонує спеціальний режим низького енергоспоживання, оптимізований для міжчіпових інтерфейсів.

• Аналоговий інтерфейс, що налаштовується користувачем (XADC), що містить два 12-бітні аналого-цифрові перетворювачі з частотою 1 MSPS та вбудованими датчиками температури та живлення.

• Цифровий сигнальний процесор з помножувачем 25 x 18, 48-бітним акумулятором та попереднім суматором для високопродуктивної фільтрації, включаючи оптимізовану симетричну коефіцієнтну фільтрацію.

• Потужні блоки керування тактовою частотою (CMT), що поєднують блоки фазового автопідстроювання частоти (PLL) та змішаного режиму керування тактовою частотою (MMCM) для високої точності та низького джиттера.

• Швидке розгортання вбудованої обробки даних за допомогою процесора MicroBlaze™.

• Інтегрований блок для PCI Express® (PCIe), для конструкцій кінцевих точок та кореневих портів до x8 Gen3.

• Широкий вибір варіантів конфігурації, включаючи підтримку стандартних пам'ятей, 256-бітове AES-шифрування з автентифікацією HMAC/SHA-256 та вбудоване виявлення та виправлення SEU.

• Низька вартість, дротяне з'єднання, оголений кристал фліп-чіп та висока цілісність сигналу, що забезпечує легку міграцію між членами сімейства в одному корпусі. Всі корпуси доступні у безсвинцевому варіанті, а деякі корпуси - у свинцевому варіанті.

• Розроблено для високої продуктивності та найнижчого енергоспоживання завдяки техпроцесу 28 нм, HKMG, HPL, технології напруги ядра 1,0 В та опції напруги ядра 0,9 В для ще нижчого енергоспоживання.