Програмована вентильна матриця XC6SLX75-2FGG484C

♠ Опис продукту

| Атрибут продукту | Значення атрибута |

| Виробник: | Ксілінкс |

| Категорія продукту: | FPGA - програмована вентильна матриця |

| RoHS: | Деталі |

| Серія: | XC6SLX75 |

| Кількість логічних елементів: | 74637 ЛЕ |

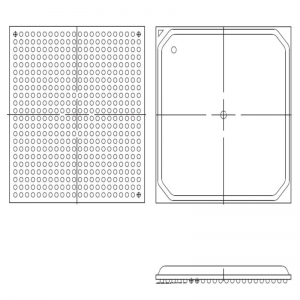

| Кількість вводів/виводів: | 280 вводів/виводів |

| Напруга живлення - Мін.: | 1,14 В |

| Напруга живлення - макс.: | 1,26 В |

| Мінімальна робоча температура: | 0°C |

| Максимальна робоча температура: | +85°C |

| Швидкість передачі даних: | - |

| Кількість приймачів: | - |

| Стиль монтажу: | Поверхневий монтаж/поверхневий монтаж |

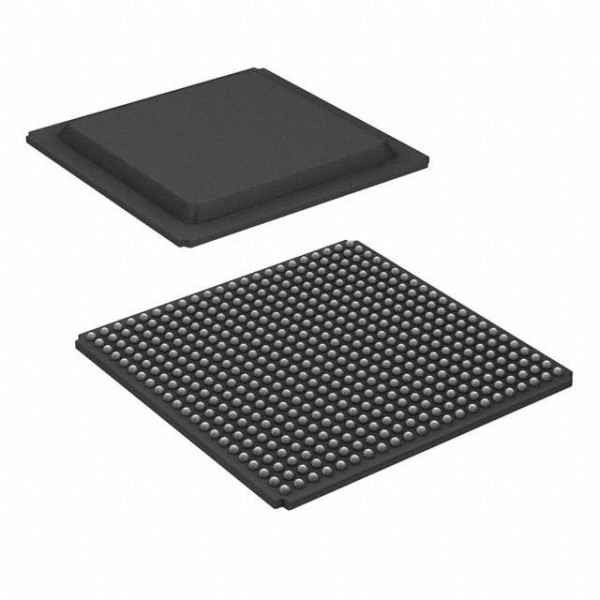

| Пакет / Корпус: | FCBGA-484 |

| Бренд: | Ксілінкс |

| Розподілена оперативна пам'ять: | 692 кбіт/с |

| Вбудована блокова оперативна пам'ять - EBR: | 3096 кбіт/с |

| Максимальна робоча частота: | 1080 МГц |

| Чутливість до вологи: | Так |

| Кількість блоків логічного масиву - LAB: | 5831 ЛАБ |

| Робоча напруга живлення: | 1,2 В |

| Тип продукту: | FPGA - програмована вентильна матриця |

| Кількість у заводській упаковці: | 1 |

| Підкатегорія: | Програмовані логічні мікросхеми |

| Торгова назва: | Спартанський |

| Вага одиниці: | 1,662748 унції |

♠ Огляд родини Spartan-6

Сімейство Spartan®-6 забезпечує провідні можливості системної інтеграції з найнижчою загальною вартістю для великогабаритних застосувань. Сімейство, що складається з тринадцяти елементів, забезпечує розширену щільність від 3840 до 147 443 логічних елементів, з вдвічі меншим енергоспоживанням порівняно з попередніми сімействами Spartan та швидшим, більш повним підключенням. Побудоване на основі зрілої 45-нм низькоенергетичної мідної технології, яка забезпечує оптимальний баланс вартості, потужності та продуктивності, сімейство Spartan-6 пропонує нову, більш ефективну, дворегістрову 6-вхідну таблицю пошуку (LUT) та багатий вибір вбудованих блоків системного рівня. До них належать 18 Кбіт (2 x 9 Кбіт) блочна оперативна пам'ять, зрізи DSP48A1 другого покоління, контролери пам'яті SDRAM, покращені блоки керування тактовою частотою змішаного режиму, технологія SelectIO™, оптимізовані за енергоспоживанням високошвидкісні блоки послідовних приймачів, сумісні з PCI Express® блоки кінцевих точок, розширені режими керування живленням системного рівня, параметри автоматичного визначення конфігурації та покращена безпека IP із захистом AES та Device DNA.

Ці функції забезпечують недорогу програмовану альтернативу користувацьким ASIC-продуктам з безпрецедентною простотою використання. ПЛІС Spartan-6 пропонують найкраще рішення для великогабаритних логічних проектів, орієнтованих на споживача проектів цифрових сигнальних процесорів (DSP) та економічно чутливих вбудованих застосувань. ПЛІС Spartan-6 – це програмована кремнієва основа для цільових платформ проектування (Targeted Design Platforms), що забезпечують інтегровані програмні та апаратні компоненти, що дозволяють розробникам зосередитися на інноваціях, щойно починається їхній цикл розробки.

• Сімейство «Спартан-6»:

- FPGA Spartan-6 LX: оптимізована логіка

- FPGA Spartan-6 LXT: Високошвидкісне послідовне з'єднання

• Розроблено для низької вартості

- Кілька ефективних інтегрованих блоків

- Оптимізований вибір стандартів вводу/виводу

- Шахматні колодки

- Пакети з пластикового дротяного з'єднання великого об'єму

• Низька статична та динамічна потужність

- 45-нм техпроцес, оптимізований для вартості та низького енергоспоживання

- Режим глибокого сну для нульового енергоспоживання

- Режим призупинення підтримує стан і конфігурацію з багатоконтактним пробудженням, покращенням керування

- Напруга ядра 1,0 В з меншим енергоспоживанням (тільки FPGA LX, -1L)

- Високопродуктивна напруга ядра 1,2 В (ПЛІС LX та LXT, класи швидкостей -2, -3 та -3N)

• Багатовольтні, багатостандартні інтерфейсні банки SelectIO™

- Швидкість передачі даних до 1080 Мбіт/с на кожен диференціальний ввід/вивід

- Вибір вихідного струму, до 24 мА на контакт

- Стандарти та протоколи від 3,3 В до 1,2 В/О

- Недорогі інтерфейси пам'яті HSTL та SSTL

- Відповідність вимогам гарячої заміни

- Регульована швидкість зміни сигналу вводу/виводу для покращення цілісності сигналу

• Високошвидкісні послідовні приймачі GTP у ПЛІС LXT

- До 3,2 Гбіт/с

- Високошвидкісні інтерфейси, включаючи: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort та XAUI

• Інтегрований блок кінцевої точки для конструкцій PCI Express (LXT)

• Підтримка недорогої технології PCI®, сумісної зі специфікацією 33 МГц, 32- та 64-розрядних процесорів.

• Ефективні зрізи DSP48A1

- Високопродуктивна арифметика та обробка сигналів

- Швидкий множник 18 x 18 та 48-бітний акумулятор

- Можливість конвеєрної та каскадної обробки

- Попередній суматор для допомоги у фільтрації програм

• Блоки вбудованого контролера пам'яті

- Підтримка DDR, DDR2, DDR3 та LPDDR

- Швидкість передачі даних до 800 Мбіт/с (пікова пропускна здатність 12,8 Гбіт/с)

- Багатопортова структура шини з незалежним FIFO для зменшення проблем із синхронізацією проектування

• Багаті логічні ресурси зі збільшеною логічною ємністю

- Додаткова підтримка регістра зсуву або розподіленої оперативної пам'яті

- Ефективні 6-вхідні LUT покращують продуктивність та мінімізують енергоспоживання

- LUT з подвійними тригерами для застосувань, орієнтованих на конвеєр

• Блочна оперативна пам'ять із широким діапазоном деталізації

- Швидка блочна оперативна пам'ять з можливістю запису байтів

- Блоки по 18 Кбіт/с, які можна за бажанням запрограмувати як дві незалежні блочні оперативні пам'яті по 9 Кбіт/с

• Плитка керування годинником (CMT) для покращеної продуктивності

- Низький рівень шуму, гнучкий тактовий режим

- Цифрові менеджери годинника (DCM) усувають перекіс годинника та спотворення шпаруватості

- Фазово-підстроєні контури (ФАПЧ) для низького джиттера

- Синтез частоти з одночасним множенням, діленням та зсувом фази

- Шістнадцять мереж глобального годинника з низькою асиметрією

• Спрощена конфігурація, підтримує недорогі стандарти

- 2-контактна конфігурація з автоматичним визначенням

- Широка підтримка сторонніх SPI (до x4) та NOR флеш-пам'яті

- Багатофункціональна платформа Xilinx Flash з JTAG

- Підтримка MultiBoot для віддаленого оновлення з кількома бітовими потоками, використовуючи сторожовий захист

• Посилений захист дизайну

- Унікальний ідентифікатор ДНК пристрою для автентифікації дизайну

- Шифрування бітового потоку AES у більших пристроях

• Швидша вбудована обробка даних завдяки покращеному, недорогому програмному процесору MicroBlaze™

• Провідні в галузі інтелектуальні та еталонні розробки